Journal of Huaqiao University (Natural Science)

文章编号: 1000-5013(2013)01-0026-04

## 基于 DM6437 的图像采集与 VGA 显示系统设计

花魁1,沈捷1,2,周柱1,张湜1

(1. 南京工业大学 自动化与电气工程学院, 江苏 南京 210009;

2. 东南大学 复杂工程系统测量与控制教育部重点实验室, 江苏 南京 210096)

摘要: 以 TMS320 DM6437 为主控芯片,讨论一种基于 DSP/BIOS 类/微型驱动模型的图像采集与视频图形阵列(VGA)显示系统设计方法. 在类/微型驱动模型中将驱动模型分为与硬件无关(类驱动)和与硬件相关(微型驱动)的两层,应用程序通过调用类驱动来间接调用微型驱动函数,从而达到控制图像采集及 VGA 显示的目的. 实验结果表明:系统可以很好地实现 DM6437 的图像采集与 VGA 显示,达到了理想效果.

关键词: TMS320 DM6437 芯片;图像采集;类驱动;微型驱动;视频图形阵列

中图分类号: TN 911.73

文献标志码: A

视频图形阵列(VGA)是一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点. VGA 技术在一些既要求显示高分辨率图像又无需使用计算机的设备上应用却很少见到. 一个完整的图像处理系统不但要具备图像数据的采集功能,还应对图像进行实时显示,最重要的是完成对图像数据的算法研究. TMS320 DM6437 是美国德州仪器(TI)公司推出的一款图像处理方面的 DSP 芯片,它采用了C64<sup>+</sup>系列处理器,主频达到 600 MHz,能够快速地处理图像数据,广泛用于移动物体检测系统的设计<sup>[1]</sup>. TI公司提出了基于 DSP/BIOS 的设备驱动模型,该模型分为两层:类驱动和微型驱动,两层之间使用通用接口<sup>[2]</sup>. TI公司所有的 DSP 软件都可以在 CCS 中开发<sup>[3-5]</sup>. 应用程序只需调用类驱动的 API 函数操作微型驱动,以微型驱动控制外部设备. 本文以 DM6437 为主控芯片,讨论了一种基于 DSP/BI-OS 类/微型驱动模型的图像采集与 VGA 显示模块的实现方法.

#### 1 硬件系统结构

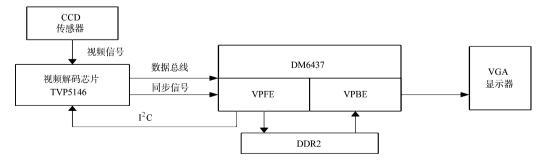

图 1 为视频采集及显示系统.系统主要包括图像采集和图像显示两个部分.图像采集模块由CCD 传感器、视频解码芯片 TVP5146 和 DM6437 的视频处理前端(VPFE)构成<sup>[6]</sup>;图像显示模块由视频处理后端(VPBE)和视频图形阵列(VGA)显示器构成.

图 1 视频采集及显示系统

Fig. 1 Video acquisition and display system

收稿日期: 2012-06-15

通信作者: 沈捷(1976-),男,副教授,主要从事模式识别系统与应用的研究. E-mail:shenjienj@163.com. 基金项目: 东南大学复杂工程系统测量与控制教育部重点实验室开放课题基金资助项目(2010A004)

DM6437 通过 I<sup>2</sup>C 总线对 TVP5146 芯片进行配置,例如输入时钟频率、视频制式及视频输入格式等. TVP5146 芯片在同步信号的控制下,通过 8 位数据线将采集的图像数据,以 YCbCr 视频数据流的格式传输至 VPFE;然后,由 VPFE 的 CCDC 模块对图像进行预处理,并存入 DDR2 中. 此外, DM6437的视频处理后端(VPBE)读取存储在 DDR2 中的视频图像信号,将数字信号转换成模拟信号在行同步和场同步信号下完成 VGA 的显示.

#### 2 软件系统设计

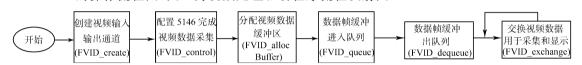

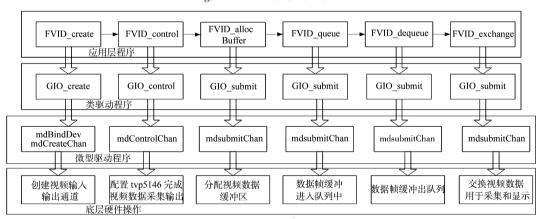

首先,通过 FVID\_create 函数创建通道,函数返回的句柄作为下一步 FVID\_control 的参数;然后,调用 FVID\_control 函数向微型驱动发送控制命令,如发送采集图像的命令,并利用 FVID\_allocBuffer 函数分配缓冲区,以及 FVID\_queue 将空 buffer 加入 buffer 队列,等待驱动程序填入图像数据;接着,FVID\_dequeue 将存有图像数据的 buffer 从队列中取出.之所以用 FVID\_dequeue 函数将队列中的首个 buffer 释放出来,是为了接下来作为 FVID\_exchange 函数的起始参数,表示当前正在使用的 buffer.最后进入无限循环 While(1),利用 FVID\_exchange 函数保证视频数据能够实时地供应用程序使用.图 2 为 FVID APIs 的操作流程图,图 3 为视频处理驱动程序流程映射图.

图 2 FVID APIs 流程图

Fig. 2 FVID APIs flow chart

图 3 视频处理驱动程序流程映射图

Fig. 3 Mapping graph of video processing driver

#### 2.1 视频数据的采集系统驱动程序

图像采集模块由 CCD 传感器和 DM6437 的 VPFE 构成.由 CCD 传感器将图像光信号装换成电信号,在像素时钟和同步控制线的控制下,通过并行数据线传输给 DM6437 的 VPFE 模块的 CCDC 控制器,并存入 DDR2 内存中.为了实现视频数据的采集,需要在类驱动及微型驱动的 DDC 层设置 CCDC 模块的相关寄存器.部分类驱动及微型驱动代码设置如下:

GIO\_Handle hGioVpfeCcdc; //定义采集句柄

PSP\_VPFE\_TVP5146\_ConfigParams tvp5146Params=VID\_PARAMS\_TVP5146\_

DEFAULT; //通过配置 tvp5146 设置图像采集模式

hGioVpfeCcdc=FVID\_create("/VPFE0",IOM\_INOUT,NULL,

&vpfeChannelParams, NULL); // 创建视频输入通道

LLC\_setHDVDToSyncWithExtHDVD(ccdcHandleCC-)regs); //vd/hd 信号使能

$FVID\_control(hGioVpfeCcdc, VPFE\_ExtVD\_BASE + PSP\_VPSS\_EXT\_VIDEO\_I) \\$

DECODER\_CONFIG, & tvp5146Params); //开始采集图像

#### 2.2 VGA 显示系统驱动程序设计

模式为 RGB

VGA 显示器的显示采取的是逐行扫描的方式,即扫描从屏幕的左上方开始,从左到右,从上到下逐行扫描.每扫完一行,电子束回到屏幕左边下一行的起始位置,期间对电子束进行行消隐.每行结束时,用行同步信号进行行同步,扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐并预备进行下一次的扫描.

一幅图要想在 VGA 接口的显示器上显示,主要需要行同步信号、场同步信号和 R,G,B 信号. 行、场同步信号必须按照 VGA 接口协议的时序标准. 这部分由 DM6437 控制输出,模拟 RGB 信号由视频处理后端(VPBE)中的 VENC 模块控制输出. 为了实现视频数据的 VGA 显示需要在类驱动以及微型驱动的 DDC 层设置 VENC 模块的相关寄存器. 部分类驱动及微型驱动代码设置如下:

```

GIO_Handle hGioVpbeVid0;

GIO_Handle hGioVpbeVenc; //定义显示句柄

vpbeVencConfigParams. displayStandard=PSP_VPBE_DISPLAY_525P_PROGRES-

SIVE_COMPONENT; //在应用程序中设置显示标准.

通过调用 DDC 层中自己编写的 switch 语句可以设置其他显示标准. switch 语句如下:

switch(vencConfigParams-)displayStandard) // 在应用程序调用 DDC 层中的相应 case 语句

可以选择不同显示标准

{

case PSP_VPBE_DISPLAY_NTSC_INTERLACED_COMPOSITE:

《相关寄存器设置

}

break:

case PSP_VPBE_DISPLAY_525P_PROGRESSIVE_COMPONENT:

{LLC_setVideoOutputTYP_525p_HDTV(vencHandleCVMP-) VencRegs);

LLC_setDigitalVidOutModeRGB666_18BIT(vencHandleCVMP-)VencRegs);

//通过 DDC 层调用 LLC 层中的函数从而设置相关寄存器

break;

hGioVpbeVenc=FVID_create("/VPBE0",IOM_INOUT,NULL,&vpbeChannelParams,

NULL); // 创建显示通道

result=FVID_allocBuffer(hGioVpfeCcdc, & frameBuffTable[i]); //分配采集和显示

缓冲区

FVID_queue(hGioVpbeVid0, frameBuffTable[i]); //数据帧缓冲进入队列

FVID_dequeue(hGioVpfeCcdc, & frameBuffPtr); //数据帧缓冲进出队列

FVID_exchange(hGioVpfeCcdc, & frameBuffPtr); //交换显示缓冲区

FVID_exchange(hGioVpbeVid0, & frameBuffPtr); //用于采集和显示

LLC_setSyncPinIOOutput(vencHandleCVMP-)VencRegs); // 通过 DDC 层调用 LLC

层中的函数 CSL_FINST(vencRegs-) VIDCTL, VENC_VIDCTL_SYDIR, OUT-PUT),

将控制行同步信号和场同步信号的管脚设置为输出

LLC_setEnableVerticalSyncOutput(vencHandleCVMP->VencRegs);

LLC_setEnableHorizontalSyncOutput(vencHandleCVMP-)VencRe; // 设置 VENC 模块

的 SYNCCTL 寄存器的 SYEV 和 SYEH 位为 ON,最终输出场同步信号和行同步信号

```

LLC\_setRGBModeSelectForComponentOutput(vencHandleCVMP-)VencRegs); //输出

LLC\_setDacCOutVidFormatR (vencHandleCVMP->VencRegs);

LLC\_setDacCOutVidFormatG (vencHandleCVMP->VencRegs);

LLC\_setDacCOutVidFormatB(vencHandleCVMP-)VencRegs); //通过 DDC 层分别调用 LLC 层中的 3 个函数,设置 VENC 模块 DACSEL 寄存器的 DA0S 位为 5h,DA1S 位为 3h 和 DA2S 位为 5h,分别输出 R,G,B 信号.

#### 3 实验测试

系统采用 PAL 制式的 CCD 模拟摄像头,CETEK-DM6437-A 评估板,以及 XDS560U 仿真器. 视频

图像的采集频率为 25 帧·s<sup>-1</sup>,图像大小为 720 px×480 px. 在 CCS3.3 编译环境下将工程文件(. pjt)下载到 DSP中. 通过 CCD 摄像头采集到的实时视频图像,如图 4 所示. 从图 4 可知:实时视频图像清晰,动态画面稳定并且流畅,达到预期效果.

### 4 结束语

介绍一种基于 DSP/BIOS 类/微型驱动模型的视频图像采集及 VGA 显示方法,并详细介绍了驱动程序的开发过程.在应用程序中只需修改相应的参数,就可以实现不同格式视频数据的采集与显示,缩短了开发时间,提高代码的可移植性.

图 4 图像采集与显示 Fig. 4 Image acquisition and display

#### 参考文献:

- [1] YIN Zhi-jian, HE Yun-fei, XIONG Chun-ru, et al. The design of moving objects detection system based on DM6437 [C]// International Conference on Computer Science and Service System, Nanjing: IEEE, 2011;27-29.

- 「2] 王军宁,何迪,马娟, TI DSP/BIOS 用户手册与驱动开发「M],北京,清华大学出版社,2004.

- [3] 李方慧,王飞,何佩琨. TMS320C6000 系列 DSPs 原理和应用[M]. 2 版. 北京:电子工业出版社,2003.

- [4] 彭启琮, 管庆. DSP 集成开发环境: CCS 及 DSP/BIOS 的原理与应用[M]. 北京:电子工业出版社, 2004.

- [5] 彭启琮. 达芬奇技术: 数字图像/视频信号处理新平台[M]. 北京:电子工业出版社,2008.

- [6] 吕颖利. DSPC6000 环境下视频处理驱动软件设计与研究[D]. 西安:西安科技大学,2009.

# Image Acquisition and VGA Display System Design Based on DM6437

HUA Kui<sup>1</sup>, SHEN Jie<sup>1,2</sup>, ZHOU Zhu<sup>1</sup>, ZHANG Shi<sup>1</sup>

(1. School of Automation and Electrical Engineering, Nanjing University of Technology, Nanjing 210009, China;

2. Key Laboratory of Measurement and Control of Complex Systems of

Engineering of Ministry of Education, Southeast University, Nanjing 210096, China)

**Abstract:** In this system, TMS320 DM6437 is taken for the master chip. A method which based on DSP/BIOS class/mini driver model is discussed, so the image acquisition and display in video graphics array (VGA) monitor is realized. The class/mini driver is divided into two layers. One is device-independent layer (class driver) and the other is device-specific layer (mini driver). In order to control the image acquisition and display in VGA monitor, class driver API is used to call the mini driver function indirectly. The results of the experiments based on DM6437 system are shown that the method can achieve ideal effect of image acquisition and display in VGA monitor.

Keywords: TMS320 DM6437 chip; image acquisition; class driver; mini driver; video graphics array

(责任编辑: 黄晓楠 英文审校: 吴逢铁)