Journal of Huaqiao University (Natural Science)

文章编号: 1000-5013(2012)01-0023-04

# CMOS全差分跨导运算放大器的建模与设计

傅文渊1,2,凌朝东1,2

(1. 华侨大学 信息科学与工程学院, 福建 厦门 361021;

2. 厦门市专用集成电路系统重点实验室,福建 厦门 361008)

摘要: 研究带增益自举结构的高速、高增益跨导运算放大器,并对增益自举运放建立数学模型和进行 Matlab 仿真验证. 将设计的运算放大器应用于 12 bit 100 M SPS 模数转换器(ADC)中,可得到辅助运放的带宽的最佳设计. 仿真结果表明:添加辅助运放后,可以达到 106 dB 的增益,增加了 55 dB;添加辅助运放后的主极点较之前大大减小,次主极点略有减小,但辅助运放的添加并不会影响运放使用时的速度.

关键词: 运算放大器;全差分跨导;增益自举;模数转换器;互补金属氧化物半导体

中图分类号: TP 722.770.2

文献标志码: A

在高速、高精度流水线型模数转换器中,模拟信号经采样保持后得到的信号将经过多级流水线级进行处理.每个流水线级的输入信号经过 Flash 模数转换器(ADC)得到对应的数字码,而其中无法被分辨的残余信号被本级放大后再输出到下一级进行处理[1],得到残差信号并将其放大的电路即为残差放大器(MDAC). 残差放大器是以运放为基础搭建的开关电容放大器,其精度和速度直接影响到整个流水线 ADC 的速度和精度.为满足高精度,要求运算放大器必须具有非常高的开环增益,倾向于选择多级结构和长沟道器件[2];为了实现高速,要求运算放大器具有大的单位增益带宽,而单级运放结构和短沟道器件是能够满足的[3].然而,两者不可避免会产生冲突,解决问题的关键是寻找一种满足要求的折衷结构.增益自举技术大大增加了输出阻抗以提高运放增益[4],但并不增加额外的共源共栅器件,不会影响主运放的输出摆幅、单位增益带宽.基于增益自举结构的运算放大器[5]利用辅助运放来提高增益,且不会影响运放的输出共模范围和速度,适用于高速、高精度模数转换器.本文基于 12 bit 100 M SPS 模数转换器,设计全差分跨导运算放大器,并对增益自举运放建立数学模型和 Matlab 仿真验证.

## 1 增益自举运放

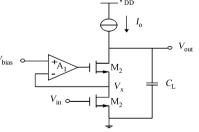

采用增益自举运算放大器结构,其频率响应特性近似为单极点系统,并能实现高增益、大带宽和快速建立时间,如图 1 所示. 该运算放大器由一个套筒式共栅共源主运———V<sub>DD</sub>

放和两个辅助运放构成.

$M_1$  的工作像一个反馈电阻,检测输出电流并把电流转换为电压;然后,将电压经辅助放大器  $A_1$  通过  $M_2$  的栅端反馈到输出电流  $V_{\text{bias}}$  上,以此减小  $M_2$  漏极电压的变化对  $V_x$  的影响,从而使输出电流更加稳定,得到更高的输出阻抗.

设辅助运放直流增益为  $A_{\text{add}}$ ,根据电流-电压反馈原理,电路的输出阻抗增大了  $A_{\text{add}}$ 倍.因此,主运放的套筒式共栅共源结构加上辅助运放后,其运放的直流增益增大为

$$A_{\text{v,tot}} = g_{\text{m}_2} [g_{\text{m}_3} r_{\text{o}_3} r_{\text{o}_2} A_{\text{v,add,p}} /\!/ g_{\text{m}_4} r_{\text{o}_4} r_{\text{o}_5} A_{\text{v,add,n}}].$$

(1)

图 1 增益自举运放结构图 Fig. 1 Structure of gain-boost operational amplifier

**收稿日期:** 2011-01-13

通信作者: 傅文渊(1983-),男,助教,主要从事信号处理和混合信号电路的研究. E-mail:fwy@hqu. edu. cn.

基金项目: 国家自然科学基金资助项目 (60772164); 福建省自然科学基金资助项目 (T0850005)

### 2 运放系统的建模

#### 2.1 辅助放大器

在增益自举技术中,辅助运放 A<sub>1</sub> 的添加会影响主运放的性能,因此需要分析两者的关系,使整体运放达到最好的指标,考虑整体运放的开环特性,为简单计,设辅助运放为单极点系统,其传输函数为

$$A_{\text{add}}(s) = \frac{A_{\text{add}}}{(1 + s/\omega_1)}.$$

(2)

此时,增益自举运放的增益可以表示为

$$A_{\text{tot}}(s) = \frac{V_{\text{ort}}(s)}{A_{\text{in}}} = -g_{m_1} [R_{\text{out}}(s) // \frac{1}{sC_L}]. \tag{3}$$

式(3)中 $:g_{m_1}$ 为输入管  $M_1$  管跨导 $:C_L$  为负载电容 $:R_{out}(s)$ 是频率的函数 $:R_{out}(s)$ 的表示式为

$$R_{\text{out}}(s) = g_{\text{m}_2} r_{\text{ds}_2} r_{\text{ds}_1} [1 + A_{\text{add}}(s)]. \tag{4}$$

式(4)中: $g_{m_2}$ 为  $M_2$  管跨导; $r_{ds_1}$ 与  $r_{ds_2}$ 分别为  $M_1$ 与  $M_2$  管的输出阻抗.将式(4)代入式(3),可得到

$$A_{\text{tot}}(s) = \frac{-g_{m_1}}{sC_L + 1/R_{\text{out}}(s)} = \frac{-g_{m_1}[1 + A_{\text{add}}(s)]}{sC_L[1 + A_{\text{add}}(s)] + \frac{1}{g_{m_1}r_{\text{obs}}r_{\text{obs}}}}.$$

(5)

把式(2)代入式(5)并化简,可得到总的开环增益为

$$A_{\text{tot}}(s) \approx \frac{-g_{\text{m}_{1}}(A_{\text{add}} + s/\omega_{1})}{s^{2} \frac{C_{L}}{\omega_{1}} + s(A_{\text{add}}C_{L} + \frac{1}{g_{\text{m}_{2}}r_{\text{ds}_{1}}\omega_{1}}) + \frac{1}{g_{\text{m}_{2}}r_{\text{ds}_{2}}r_{\text{ds}_{1}}}}.$$

(6)

从式(6)可以看到,增益自举运放存在一个左半平面零点,其值等于辅助运放的单位增益带宽  $(W_{GB})$ ,即  $\omega_Z = A_{add}\omega_1 = W_{GB\,add}$ .由式(6)可以推导出其主极点和次主极点分别为

$$p_0 \approx \frac{1}{g_{\rm m_2} r_{\rm ds_2} r_{\rm ds_1} (1 + A_{\rm add}) C_L},$$

(7)

$$p_1 \approx A_{\rm add}\omega_1 + \frac{1}{g_{\rm m_a}r_{\rm ds_a}r_{\rm ds_b}C_L}.$$

(8)

式(8)中:第1项为辅助运放的单位增益带宽;第2项为没有添加增益自举技术时主运放的主极点. 当次主极点的第1项远大于第2项时,第2个极点  $p_1 \approx A_{\rm add} \omega_1 \approx \omega_Z$ . 由此可以看出,辅助运放对整体运放产生了位置很相近的一个零极点对.

进一步考虑其闭环特性. 在首级残差放大器中,运算放大器处于反馈系数为 $\beta$ 的闭环结构中. 此时,闭环传输函数可表示为

$$A_{c1}(s) = \frac{A_{tot}(s)}{1 + \beta A_{tot}(s)} = \frac{(s - z_0)k_1}{(s - p_0)(s - p_1) + \beta(s - z_0)k_1}.$$

(9)

式(9)中 $:z_0$  为闭环零点 $:k_1$  为  $M_1$  管跨导 $:p_0,p_1$  为运放的极点. 系统的阶跃响应为

$$V_{\text{out}}(t) = V_0(1 - m_1 \exp(-t/\tau_1) + m_2 \exp(-t/\tau_2)). \tag{10}$$

式(10)中:

$$\tau_1 = \frac{1}{\beta \cdot W_{\text{GB main}}}; \tau_2 \approx \frac{1}{W_{\text{GB add}}}; m_1 \approx k_1; m_2 \approx \frac{(p_1 + 3p_0 - k_1\beta)k_1}{p_1 - p_0 + k_1\beta}.$$

从式(10)中可以看出,零极点对的存在给运放的建立特性带来了影响.为了尽量减小其影响,必须

使  $au_1 > au_2$ ,则要求 eta •  $W_{ ext{GB main}} < W_{ ext{GB add}}$ ,同时确保  $V_{ ext{out}}$ 数值有效,则有  $\ln(rac{m_1}{m_2}) < rac{1}{ au_1} + rac{1}{ au_2}$ . 由此可得

$$\tau_2 > 2\ln(\frac{m_2}{m_1}) = 2\ln(\frac{p_1 + 3p_0 - k_1\beta}{p_1 - p_0 + k_1\beta}) \approx 2\ln(\frac{p_1 + 3p_0}{p_1 - p_0}). \tag{11}$$

即有

$$\beta W_{\rm GB\,main} < W_{\rm GB\,add} < \frac{1}{2} \ln(\frac{p_1 + p_0}{p_1 - 3\,p_0}). \tag{12}$$

当满足上述要求时,辅助运放的频率特性对整个放大器的频率特性没有太大的影响.增益自举的单位增益带宽主要由主运放的单位增益带宽决定,可表示为

$$W_{\rm GB} = \frac{g_{\rm main}}{2\pi L_{\rm G}}.\tag{13}$$

#### 2.2 Matlab 仿真

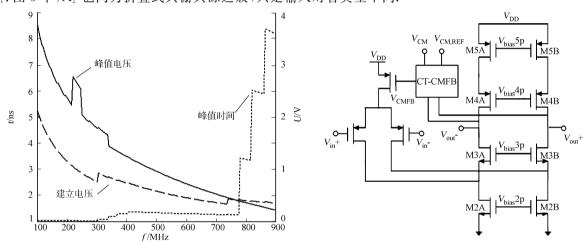

针对辅助运算放大器的主极点,编写 Matlab 程序,得出辅助运放的主极点和整体运放的建立时间、峰值电压和峰值时间的关系图,如图 2 所示. 由图 2 可知,当辅助运放的主极点增大时,运放的峰值时间将减少,且减少趋势逐步降低;在 300~750 MHz 时,峰值时间变化最小. 同时,运放的峰值电压随着辅助运放主极点增大而增加.

在 320~890 MHz 之间,运放的建立时间随着辅助运放主极点的增加而减少,但变化幅度较少(低于 0.003 7%). 因此,可以得出辅助运放的主极点在 320~890 MHz 之间变化时,对增益自举运算放大器的建立时间影响不大,而在 220~230 MHz 之间,运放建立时间减少 1 ns,变化幅度较为剧烈(10%). 此时,辅助运放的主极点将对整体运放产生迟滞作用,增大整体运放的建立时间. 由此得到设计时在满足式(13)条件的基础上,辅助运算放大器的单位增益带宽不需太大,可以得到功耗和速度的优化.

除了考虑辅助运放的频域、时域特性外,还必须考虑到其对整体运放共模输入范围和输出摆幅的影响<sup>[6-7]</sup>.辅助运算放大器采用折叠型共栅共源运放结构,不会影响整体运放的输出摆幅.由于两个辅助输入共模电平的不同,其输入管分别为 PMOS 管和 NMOS 管.图 3 是输入对管为 NMOS 管的辅助运放 A<sub>1</sub>.图 3 中,A<sub>2</sub> 也同为折叠式共栅共源运放,只是输入对管类型不同.

图 2 辅助运放主极点的 Matlab 仿真 Fig. 2 Matlab simulition of auxiliary operational amplifier dominant pole

图 3 辅助运放结构 Fig. 3 Structure for auxiliary operational amplifier

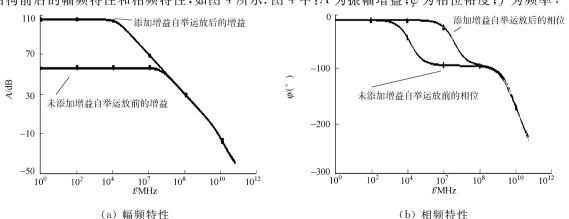

#### 2.3 HSPICE 仿真结果

运放仿真性能指标:开环增益为 102~dB;单位增益带宽为 1.95~GHz;相位裕度为  $62^{\circ}$ ;建立时间为 4.8~ns;负载电容为 3.5~pF;供电电源为 3.3~V. 在有、无增益自举结构情况下,套筒运放在添加增益自举结构前后的幅频特性和相频特性,如图  $4~m\pi$ . 图  $4~m\pi$ . 图  $4~m\pi$ .

图 4 套筒运放在添加增益自举结构前后的幅频/相频特性对比

Fig. 4 Contrast to the character of amplitude and phase when added to cascade operational amplifier

从图 4 中可知,仿真结果和理论研究基本相符. 在未加增益自举结构时,运放仅能达到 51 dB 的增益;添加辅助运放后,可以达到 106 dB 的增益,满足首级 MDAC 对运放增益的要求.

在图 4 中还可以看到,添加辅助运放后的主极点较之前大大减小,次主极点略有减小.这是由于辅助运放的添加增大了该点的寄生电容.但是,由于增益的提高,运放的单位增益带宽及相位裕度在两种情况下基本不变,证明辅助运放的添加并不会影响运放使用时的速度.

### 3 结束语

系统分析了在 Pipeline ADC 设计中增益自举结构的跨导运算放大器特性,揭示了辅助运算放大器 对整体运算放大器带宽影响的数学机理,对模数混合信号电路设计者有较大的参考价值.

#### 参考文献:

- [1] GALTON S E. A digitally enhanced 1, 8-V 15-bit 40-MSample/s CMOS Pipelined ADC[J]. IEEE Journal of Solid-State Circuits, 2004, 39(12):2126-2138.

- [2] QUINN P J, VAN ROERMUND A H M. Design and optimization of multi-bit front-end stage and scaled back-end stages of pipelined ADCs[J]. IEEE ISCAS, 2005, 40(3):1964-1967.

- [3] BULT K, GEELEN G J G M. A fast-settling CMOS op amp for SC circuits with 90-dB DC gain[J]. IEEE Journal of Solid-State Circuits, 1990, 25(6): 1379-1384.

- [4] LOTFI R, TAHERZADEH-SANI M, AZIZI MY, et al. Systematic design for power minimization of pipelined analog-to-digital converters[C]// International Conference on Computer Aided Design. San Jose: [s. n. ], 2003:371-374.

- [5] CHOKSI O, CARLEY R L. Analysis of switched-capacitor common-mode feedback circuit[J]. IEEE Transactions on Circuit and Systems (]]); Analog and Digital Signal Processing, 2003, 50(12)::906-917.

- [6] GRAY P R. Analysis and design of analog integrated circuits M. New York: Wiley, 2000.

- [7] 凌朝东,黄群峰,张艳红,等. 脑电信号提取专用电极芯片的设计[J]. 华侨大学学报:自然科学版,2007,28(3):260-263.

# Design and Modeling of a CMOS Fully Differential Transconductance Operational Amplifier

FU Wen-yuan<sup>1,2</sup>, LING Chao-dong<sup>1,2</sup>

- (1. College of Information Science and Engineering, Huaqiao University, Xiamen 361021, China;

- 2. Key Laboratory of ASIC and System of Xiamen, Xiamen 361008, China)

**Abstract:** Research of high-speed and high-gain transconductance amplifier with the structure of gain-boost, the mathematical modeling and Matlab simulation is presented for gain-boost operational amplifier. Designed operational amplifier is used in 12 bit 100 M SPSADC, and the optimal design on the auxiliary amplifier bandwidth can be obtained. Simulation results show that gain is 106 dB which increses of 55 dB if an auxiliary operational amplifier is added. Besides, if we the auxiliary operational, dominant pole is greatly reduced and non-dominant pole slightly decreases, but the addition of auxiliary amplifier does not affect the speed of the operational amplifier.

**Keywords:** operational amplifier; fully differential transconductance; gain-boosting; analog to digital converter; complementary metal-oxide-semiconductor

(责任编辑:钱筠 英文审校:吴逢铁)