文章编号: 1000-5013(2011)06-0633-05

# 一种适用于心电信号检测的放大器设计

杨骁1,2,齐骋1,2,黄炜炜1,2,凌朝东1,2

- (1. 华侨大学 信息科学与工程学院, 福建 泉州 362021;

- 2. 厦门市 ASIC 系统重点实验室, 福建 厦门 361021)

摘要: 针对传统斩波放大器功耗较大,以及电极的直流极化电压容易使得高增益放大器进入饱和状态的问题,提出一种适合应用于心电信号的放大器.该低功耗斩波放大器电路由一个两级放大器组成,第 1 级折叠共源共栅放大器的高输出阻抗与第 1 级和第 2 级之间的密勒等效电容组成一个低通滤波器,以滤除调制噪声.采用 TSMC 0.18  $\mu$ m 1P4M 工艺,对所提出的放大器结构进行电路设计.仿真结果表明:整个放大器带宽为 0.2~170 Hz,功耗为 52  $\mu$ W,其等效输入噪声电压为 150  $\mu$ C 0.1 Hz,等效输入积分噪声为 0.68  $\mu$ C 0.1  $\mu$ C 150 Hz),具有较好的低功耗、低噪声特性.

关键词: 斩波技术;放大器;失调电压;噪声;心电信号

中图分类号: TN 722.302; R 540.4

文献标志码: A

生物电信号是一种强噪声背景下的低频微弱信号,心电信号的幅值大小为 0~5 mV,主要信号的 频率在 0.1~150 Hz 范围内. 对这些生物电信号进行采集前,必须将其进行放大且放大器的噪声必须足够小,才不至于把有用信号淹没. 所以,对于生物电信号放大器而言,低噪声是其非常重要的一个指标[1-2]. 另外,由于测量电极与生物体之间构成化学半电池,所产生的直流电压(即极化电压)最大可达 100 mV,如此高极化电压很容易使得高增益放大器进入饱和状态[3-6]. 同时,便携式生物电信号检测系统对芯片的功耗提出了很高的要求,要求低功耗来延长电池供电时间. 传统斩波放大器要求放大器的带宽大于其斩波频率,以及需要额外的低通滤波器来滤除调制噪声,其功耗往往较大. 本文在传统斩波放大器的基础上,提出了一种新型的,不需要额外低通滤波器的低功耗斩波放大器.

## 1 传统斩波放大器基本原理

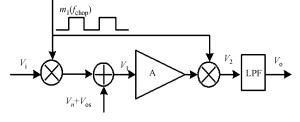

图 1 为传统斩波放大器的结构. 图 1 中: $V_i$  和  $V_o$  分别是输入和输出信号电压;A 为放大器的增益; $m_1$  是周期方波信号,其斩波频率为  $f_{chop}$ ; $V_{os}$  和  $V_n$  分别为运放的失调电压和 1/f 噪声.

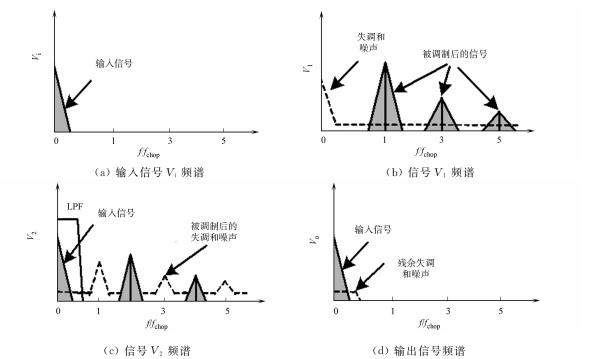

图 2 为斩波放大器的斩波调制原理·输入信号  $V_i$ (图 2a)被方波信号  $m_1$  调制到斩波频率的奇次谐波处(图 2b),输入信号及运放的失调和噪声经放大器放大后,被  $m_1$  调制,其中输入信号  $V_i$  被解调到低频处,而噪声和失调却被调制到斩波频率的奇次谐波频率处(图 2c); $V_2$  通过低通滤波器,失调和噪声被滤除掉,留下输入信号、残余失调和噪声(图 2d).

对于图 1 所示的传统斩波放大器,输入信号经

图 1 传统斩波放大器的结构

Fig. 1 Structure of traditional chopper amplifier

过第 1 个调制器后,被调制到斩波频率  $f_{\text{chop}}$  处.要使输入信号在经过放大器后不失真,放大器的带宽要大于斩波频率  $f_{\text{chop}}$  ,但这意味着大的功耗.此外,传统斩波放大器还需要低通滤波器,滤除调制到高频处

收稿日期: 2011-02-21

通信作者: 杨骁(1978-),男,讲师,主要从事模拟集成电路设计的研究. E-mail: xiaoyanghqu@hqu. edu. cn. 基金项目: 福建省自然科学基金资助项目(2010J05135); 华侨大学高层次人才科研启动项目(09BS616)

的失调和噪声分量,所以传统斩波放大器功耗较大.

图 2 斩波调制原理

Fig. 2 Chopping modulation principle

#### 2 改进的放大器结构

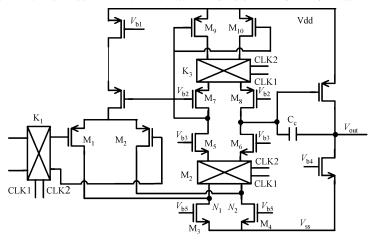

在传统斩波放大器的基础上进行改进,提出一种不需要额外低通滤波器的低功耗斩波放大器电路, 其电路如图 3 所示. 该斩波放大器采用两级运放结构,第 1 级为折叠式共源共栅结构,第 2 级为共源级 放大器. 在第 1 级放大器中,采用低电压的共源共栅电流镜来实现差分到单端输出的转换.

图 3 改进后斩波放大器电路

Fig. 3 Proposed chopper amplifier circuit

折叠式共源共栅放大器的折叠点  $N_1(N_2)$ 为一个低输出阻抗点,从运放输入端到  $N_1(N_2)$ 点的带宽很大.所以,第 2 个调制器  $K_2$  放置在折叠点  $N_1(N_2)$ 处,使输入信号被调制到频率  $f_{\text{chop}}$ 不会产生失真.被调制到频率  $f_{\text{chop}}$ 的输入信号经过调制器  $K_2$  后,被解调到基频处,而运放的失调电压和低频处的 1/f 噪声被调制到高频处.调制器  $K_2$  放置在  $N_1(N_2)$ 处另外一个好处是,由于  $N_1(N_2)$ 结点的电平较低,调制器  $K_2$  采用简单的 NMOS 开关结构,就能使得其开关的导通电阻较小,无需采用自举型开关.

在低压共源共栅电流镜中间节点(M<sub>0</sub>, M<sub>10</sub>的漏端)放置第3个调制器,应用动态元器件匹配技术来

降低电流镜失配引起的失调和电流镜的噪声. 假设第 2 级的共源极放大器的放大倍数为 A,则密勒电容  $C_c$  等效到第 1 级的输出结点的等效电容为 $(A+1)C_c$ ,即其等效电容放大了(A+1)倍. 这样采用一个小密勒电容就能得到一个大的等效电容,减小了芯片的面积.

利用第1级折叠共源共栅运放高的输出阻抗,以及等效密勒电容(A+1)C。,构建一个截止频率很

低的一阶低通滤波器,来滤除调制到高频处的失调电压和 1/f 噪声.整个斩波放大器不需要额外的低通滤波器,故减小了功耗和电路的复杂程度.另外,第2级的共源极放大器能够提供大的输出摆幅和小的输出阻抗,而且小的输出阻抗使其能够驱动小的电阻负载.

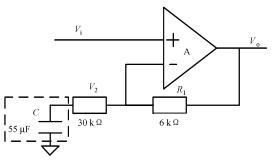

所提出适合于心电信号应用的放大器结构,如图 4 所示.图 4 中: A 为图 2 所示的斩波放大器,整个放大器配置成增益为 200 的闭环结构.从图 4 可以得到该放大器的传递函数为

图 4 改进后斩波放大器结构图

Fig. 4 Schematic of the proposed chopper amplifier

$$\frac{V_{\circ}(j\omega)}{V_{i}(j\omega)} = \frac{A(j\omega)}{R_{2} + \frac{1}{j\omega C}} \approx 1 + \frac{j\omega CR_{1}}{j\omega R_{2} + 1}.$$

$$\frac{R_{2} + \frac{1}{j\omega C}}{R_{1} + R_{2} + \frac{1}{j\omega C}} + 1$$

(1)

从式(1)可以看出,若选择电容 C,使得  $f_c = (1/2\pi)R_2C=0.1$  Hz,则该放大器对 DC 输入信号的增益为 1,而对频率 f>0.1 Hz 的信号,其增益约为 200,从而避免了由于大的电极极化电压使得放大器进入饱和状态.

### 3 电路仿真结果

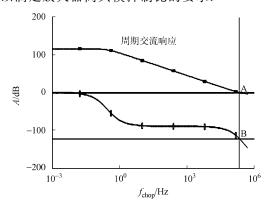

采用 TSMC 公司提供的  $0.18~\mu m$  1P4M 工艺对放大器进行电路设计,电源电压为 $\pm 1~V$ ,斩波频率  $f_{\text{chop}}$ 为 10~kHz. 图 2 中斩波放大器 A 的密勒电容  $C_c$  为 30~pF,其开环幅频响应和共模抑制比(common mode rejection ratio, CMRR)仿真,分别如图 5,6 所示. 从图 5 可知,其开环 DC 增益为 116 dB,相位裕度为  $57^{\circ}$ . 从图 6 可知:在低频处,其共模抑制比高达 107 dB;在 1.4~kHz 时,仍能达到 90~dB 共模抑制比,可以满足放大器高共模抑制比的要求.

图 5 斩波放大器 A 的幅频响应

Fig. 5 Amplitude-frequency response of chopper amplifier A

图 6 斩波放大器 A 的共模抑制比

Fig. 6 Common mode rejection ratio of chopper amplifier A

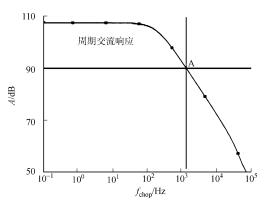

当图 2 中的时钟信号 CLK1 置为低电平,CLK2 置为高电平时,分别采用斩波技术和不采用斩波技术,斩波放大器 A 的等效输入噪声功率谱图,如图 7 所示. 从图 7 可以看出:采用斩波技术后,运放的等效输入噪声从 8  $\mu$ V@0.1 Hz 降到了 150 nV@0.1 Hz,等效输入积分噪声有效电压值(交流电有效值,即电压均方根值)从 7.6  $\mu$ V(0.1~150 Hz)降为 0.68  $\mu$ V(0.1~150 Hz),说明该斩波放大器具有较好

的低噪声特性.

图 7 斩波放大器 A 的输入等效噪声频谱图

Fig. 7 Noise performance comparison with chopping and without chopping of chopper amplifier A

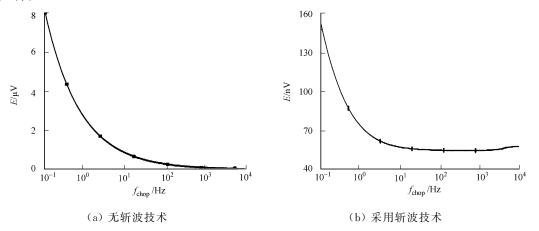

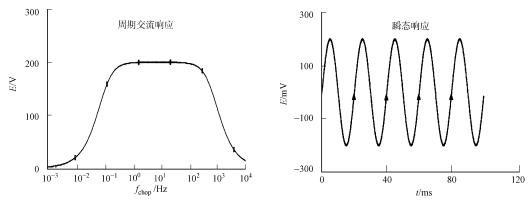

图 8 为整个放大器的幅频响应. 从图 8 可以看出:放大器幅频特性为带通特性,在 0. 2~170 Hz 频率范围内,其增益约为 200,对直流电压具有较好的抑制作用,避免了运放工作在饱和区. 对于输入信号幅值为 1 mV,频率为 50 Hz 的正弦信号,其瞬态响应如图 9 所示. 图 9 中:放大倍数为 200. 从图 9 可知:整个放大器消耗电流为 26  $\mu$ A,功耗为 52  $\mu$ W,具有较好的低功耗特性.

将所设计的改进型斩波放大器与文献[5-7]所提供的仪器仪表放大器的性能进行比较,结果如表 1 所示.表 1 中:E 为电源电压;P 为功耗;V 为输入等效噪声(交流电有效值,即电压均方根值);A 为放大器的增益.从表 1 可知:所设计的放大器结构在低功耗和低噪声方面具有较好的性能.

图 8 放大器的幅频响应

Fig. 8 Frequency response of the amplifier

图 9 放大器的瞬态响应

Fig. 9 Transient response of the amplifier

表 1 放大器的性能比较

Tab. 1 Performance comparison

| 参数              | 文献[5]的放大器                   | 文献[6]的放大器            | 文献[7]的放大器                                                        | 本文的放大器               |

|-----------------|-----------------------------|----------------------|------------------------------------------------------------------|----------------------|

| E/V             | 1                           | 1                    | 1                                                                | 2                    |

| $P/\mu { m W}$  | 165                         | 50                   | 110                                                              | 52                   |

| $V/\mu V$       | $(0.2 \sim 150 \text{ Hz})$ | 1.27<br>(0.4~200 Hz) | $\begin{array}{c} 1.64 \\ (0.1 \sim 150 \text{ Hz}) \end{array}$ | 0.68<br>(0.1~150 Hz) |

| $A/\mathrm{dB}$ | 45.6                        | 43.5                 | 38.3                                                             | 46                   |

# 4 结束语

提出一种适合于心电信号检测的放大器,并采用 TSMC 公司提供的  $0.18~\mu m$  RF 1P4M 工艺对其结构进行电路设计.该结构中的斩波放大器不需要额外的滤波器,降低了功耗,整个放大器能够抑制极化电压,避免放大器进入饱和状态.仿真结果表明:其等效输入噪声电压为 150~nV@0.1~Hz,等效输入

积分噪声为  $0.68 \mu V(0.1\sim150 \text{ Hz})$ ,具有较好的低噪声特性.整个放大器的带宽为  $0.2\sim170 \text{ Hz}$ ,功耗为  $52 \mu W$ ,所提出的放大器具有低噪声、低功耗特性,适于心电信号测量领域的应用.

#### 参考文献:

- [1] NG K A, CHAN P K. A CMOS analog frontend IC for port-able EEG/ ECG monitoring applications[J]. IEEE Transactions on Circuits and Systems (]): Regular Papers, 2005, 52(11): 2335-2347.

- [2] WITTE J F, MAKINWA K A A, HUIJSING J H. A CMOS chopper offset-stabilized opamp[J]. IEEE Journal of Solid-State Circuits, 2007, 42(7):1529-1535.

- [3] YATES D C, RODRIGUEZ-VILLEGAS E. An ultra low power low noise chopper amplifier for wireless EEG[C]//49th IEEE International Midwest Symposium on Circuits and Systems. Piscatway: IEEE, 2006:449-452.

- [4] HARRISON R R, CHARLES C. A low-power low-noise CMOS amplifier for neural recording applications[J]. IEEE Journal of Solid-State Circuits, 2003, 38(6):58-965.

- [5] NANDA C, MUKHOPADHYAY J, MANDAL D, et al. A CMOS instrumentation amplifier with low voltage and low noise for portable ECG monitoring systems[C] // 2008 International Conference on Semiconductor Electronics. Piscatway: IEEE, 2008;54-58.

- [6] WU Hong-lei, XU Yong-ping. A low-voltage low-noise CMOS instrumentation amplifier for portable medical monitoring systems [C] // The 3rd International IEEE-NEWCAS Conference. Piscatway: IEEE, 2005:19-22.

- [7] NANDA C, MUKHOPADHYAY J, MANDAL D, et al. 1 V CMOS instrumentation amplifier with high DC electrode offset cancellation for ECG acquisition systems [C] // 2010 IEEE Students' Technology Synposilum. Piscatway; IEEE, 2010; 21-25.

#### Design of Amplifier for Electroencephalogram Monitoring Applications

YANG Xiao<sup>1,2</sup>, QI Cheng<sup>1,2</sup>, WANG Wei-wei<sup>1,2</sup>, LING Chao-dong<sup>1,2</sup>

(1. College of Information Science and Engineering, Huaqiao University, Quanzhou 362021, China;

2. Key Laboratory of ASIC and System, Xiamen 361021, China)

Abstract: In order to overcome the disadvantages that the conventional chopper amplifier consumes large power and is easily saturated with the DC offset of the skin-electrode interface, a low power amplifier is presented for electroencephalogram (EEG) monitoring applications. The chopper amplifier is composed of a two-stage amplifier. The high output impedance of the first stage folded cascade amplifier and the equivalent Miller capacitance constitute together a low pass filter to filter out the modulation noise. The circuit of the amplifier is designed in TSMC 0.18  $\mu$ m 1P4M CMOS process. The bandwidth of the whole amplifier is from 0.2 Hz to 170 Hz, and the power consumption is 52  $\mu$ W. The equivalent input noise voltage of 150 nV@0.1 Hz and the input integrated referred noise voltage of 0.68  $\mu$ V from 0.1 Hz to 150 Hz are achieved. Simulation results show that the presented amplifier has characteristics of low power and low noise.

Keywords: chopping technique; amplifier; offset voltage; noise; electroencephalogram

(责任编辑: 陈志贤 英文审校: 吴逢铁)