文章编号: 1000-5013(2011)04-0478-03

## 一种新型实时时钟芯片温度误差补偿方法

赵东世1,2,凌朝东1,2,黄炜炜1,2,刘一平1,2

- (1. 华侨大学 信息科学与工程学院, 福建 泉州 362021;

- 2. 厦门市专用集成电路系统重点实验室,福建 厦门 361008)

摘要: 采用累积误差实时数字补偿技术,当温度误差累积时间达到 1 个时钟周期时,在产生 1 Hz 频率方波的计数器上采取相应的操作,少加一次或者多加一次来补偿之前的频率总误差,使实时时钟在一 $40\sim85$  °C 动态温度范围内的精度达到  $5.0\times10^{-7}$ . 仿真结果表明,1 a 的时间时钟最大误差不到 1 min,累积误差实时补偿的方法达到期望的补偿精度.

关键词: 实时时钟;温度;累积误差;频率;补偿电路

中图分类号: TN 492

文献标志码: A

#### 1 频率温度误差补偿原理

实时时钟芯片的时间误差主要来源于时钟芯片中晶振的频率误差,而晶振的频率误差主要是由于温度变化引起的.所以,把温度对晶振谐振频率所产生的误差进行有效的补偿,是提高时钟精度的关键. 石英晶体谐振频率误差补偿方法,是在晶振谐振频率随着温度的变化存在误差已知的基础上,对产生1

Hz 频率的分频计数器进行精确补偿的方法.

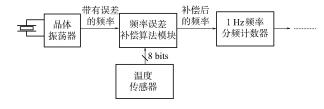

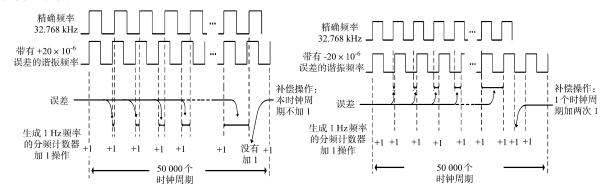

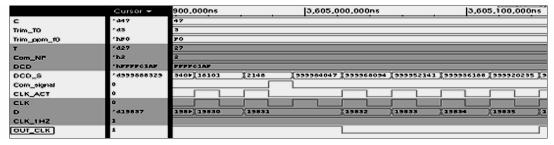

图 1 为频率温度误差补偿原理框,图 2 为温度误差补偿时序图. 当温度误差累积时间达到 1 个时钟(clock)周期时,在产生 1 Hz 频率方波的计数器上采取相应的操作,少加一次或者多加一次来补偿之前的频率总误差. 这是一种误差累积补偿方法,它具有实时补偿、精度高的优点.

图 1 频率温度误差补偿原理图

Fig. 1 Diagram of frequency-temp-error compensating

图 2 频率温度误差补偿时序图

Fig. 2 Sequence chart of frequency-temp-error compensating

收稿日期: 2011-02-02

通信作者: 凌朝东(1964-),男,教授,主要从事模拟集成电路的研究. E-mail;edac@hqu. edu. cn. 基金项目: 国家自然科学基金资助项目(60772164);福建省厦门市科技计划项目(3502Z20080010)

### 2 频率误差补偿电路设计

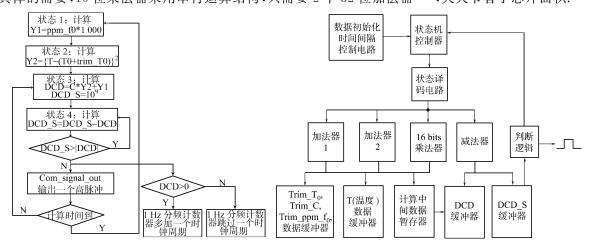

补偿电路由一个有限状态机作为控制部件,其控制流程图如图 3 所示. 为了减少数字补偿电路在版图中的面积,补偿电路的 3 次乘法运算由一个 4 状态的有限状态机控制时分复用一个 16 位乘法器. 频率误差补偿电路包含 16 位乘法器、32 位加法器及其他逻辑判断电路[1-2],其结构框图如图 4 所示. 根据具体的需要,16 位乘法器采用串行运算结构,只需要 2 个 32 位加法器[3-5],大大节省了芯片面积.

图 3 频率误差补偿电路控制流程图

Fig. 3 Flow chart of frequency-temp-error compensating circuits

图 4 频率误差补偿电路结构框图

Fig. 4 Structure drawing of frequency-temp-error compensating circuits

### 3 补偿电路仿真结果

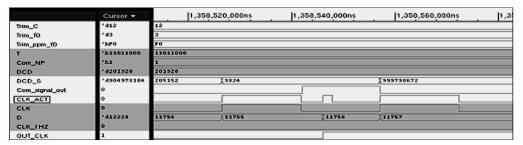

利用 Candence 软件工具对所设计温度误差补偿电路进行仿真,如图 5 所示.

(a) 仿真实验 1

(b) 仿真实验 2

图 5 温度误差补偿电路仿真

Fig. 5 Simulation of frequency-temp-error compensating

从图 5(a)的结果可知,仿真实验 1 的补偿频率误差为  $201.328 \times 10^{-6}$ . Com\_NP 为  $^{\circ}$  1  $^{\circ}$  表示时钟频率慢,循环减法运算的差(DCD\_S)小于 DCD 时,补偿输出信号 Com\_signal\_out 输出一个高脉冲. 同时,在本时钟周期内送入 1 Hz 分频计数器的时钟信号 CLK\_ACT 多产生一个上升沿,从而达到多记录一个时钟周期的补偿目的.

从图 5(b)的结果可知,仿真实验 2 的补偿频率误差为 $-15.953\times10^{-6}$ . Com\_NP 为'2'表示时钟频率快,循环减法运算的差(DCD\_S)小于 DCD 时,补偿输出信号 Com\_signal\_out 输出一个高脉冲. 同时,在本时钟周期内送入 1 Hz 分频计数器的时钟信号 CLK\_ACT 少了一个上升沿,从而达到少记录一个时钟周期的补偿目的.

在  $Trim_C = -3$ ,  $Trim_T_0 = 2$ ,  $Trim_ppm_f_0 = 18$  时, 不同温度(t)误差补偿电路计算出来的 DCD (补偿数据), 如表 1 所示.

| 表 1 温) | <b> </b> |

|--------|----------|

|--------|----------|

| T 1 1   | 0. 1         | 1. (       |            |              |          | . 1 .           |

|---------|--------------|------------|------------|--------------|----------|-----------------|

| Tab I   | Simulation   | results of | temp-error | compensating | circilit | compensate data |

| 1 40. 1 | Ommand Cloth | resures or | comp crror | Compendating | cricare  | compensate data |

| t/°C | -40    | -20    | -10    | <b>-</b> 5 | -2     | -1     | 0       |

|------|--------|--------|--------|------------|--------|--------|---------|

| DCD  | 14 366 | 70 706 | 43 826 | 32 786     | 26 930 | 25 106 | 23 346  |

| t/°C | 1      | 2      | 5      | 10         | 20     | 50     | 85      |

| DCD  | 21 650 | 20 018 | 15 506 | 9 266      | 1 586  | 16 949 | 107 666 |

#### 4 结束语

阐述的实时时钟温度补偿,是实时时钟芯片设计的一个部分. 同时,芯片内还应该有一个温度传感器电路,用来实时检测环境温度,为误差补偿电路提供温度数据.  $Trim_C$ ,  $Trim_T_0$ ,  $Trim_ppm_f_0$  中的误差可以通过更高精度的辅助测量工具测量,温度-频率数据用于拟合温度误差曲线来减小误差. 温度传感器的温度误差是本实时时钟芯片的主要误差来源.

#### 参考文献:

- [1] 夏宇闻. Verilog 数字系统设计教程[M]. 北京:北京航空航天大学出版社,2007.

- [2] 田耘,徐文波,张延伟,等. 无线通信 FPGA 设计[M]. 北京:电子工业出版社,2007.

- [3] BARR K. ASIC 设计混合信号集成电路设计指南[M]. 北京:科学出版社,2008.

- [4] RABAEY J M, CHANDRAKASAN A, NIKOLIC B. 数字集成电路: 电路系统与设计[M]. 2 版. 周润德,等译. 北京:电子工业出版社, 2004.

- [5] CILETTI M D. Verilog HDL 高级数字设计 [M]. 张雅绮, 等译. 北京: 电子工业出版社, 2004.

# A New Method to Compensate the Temperature Error in the Real Time Clock Chip

ZHAO Dong-shi<sup>1,2</sup>, LING Chao-dong<sup>1,2</sup>, HUANG Wei-wei<sup>1,2</sup>, LIU Yi-ping<sup>1,2</sup>

- (1. College of Information Science and Engineering, Quanzhou 362021, China;

- 2. Key Laboratory of ASIC and System of Xiamen, Xiamen 361008, China)

Abstract: Adopting accumulative error timely digital compensate technical, the counter which to produce 1 Hz square wave compensate the previous total error by corresponding operation that counting a more time or less time when the accumulative error up to 1 clock cycle. It can guarantee the precision of  $5.0 \times 10^{-7}$  in the temp range of  $-40 \sim 85$  centigrade. The simulation results suggest that the maximum error of the clock is less than 1 minute during 1 year, and the accumulative error timely accumulate method attains the anticipate precision.

Keywords: real time clock; temperature; accumulative error; frequency; compensate circuit

(责任编辑: 黄晓楠 英文审校: 吴逢铁)