文章编号: 1000-5013(2011)03-0280-04

# 低功耗 H. 264 Baseline 解码 IP 核设计

朱坤旺1,2,傅文渊1,2,凌朝东1,2

(1. 华侨大学 信息科学与工程学院, 福建 泉州 362021;

2. 厦门市专用集成电路系统重点实验室, 福建 厦门 361008)

摘要: 采用环形码流缓冲结构、首"1"检测方法和优先级非均匀分割技术,设计一款低功耗 H. 264 Baseline 视频解码 IP 核,并对该 IP 核进行了软件仿真和现场可编程门阵列(FPGA)验证. 结果表明,该 IP 核的功耗为 918  $\mu$ W,降低了 44%,H. 264/AVC Baseline QCIF 解码速度达到 30 帧  $\cdot$  s $^{-1}$ ,可满足实时解码需求.

关键词: H. 264 解码器; IP 核; 低功耗; 现场可编程门阵列

中图分类号: TN 764; TN 919.81

文献标志码: A

H. 264 是由 ISO/IEC 与 ITIJ-T 共同制定的新一代视频压缩编码标准,能够为低码率的传输提供较好的视频质量<sup>[1]</sup>. H. 264 采用可变大小块预测、CABAC 编码、1/4 大小运动矢量预测、去块滤波等新的编码技术<sup>[2-3]</sup>. 有关研究表明,在相同的视频质量条件下,H. 264 视频编码标准比 MPEG-4,H. 263 有着更高的压缩效率,其编码视频流与 H. 263 或 MPEG-4 Simple 编码视频流相比,平均可节省 50%的码率. 但是,它的这种优异性能是以复杂的编码算法为代价的. H. 264 在移动终端有着广泛的应用,移动终端对功耗有着严格的要求. 基于此,本文设计一款在移动终端的低功耗 H. 264 Baseline 解码 IP 核<sup>[4]</sup>.

### 1 功耗来源与分析

数字芯片的功耗主要有如下 4 种:(1) 来源于电容充放电效应的动态开关功耗;(2) 反向偏置 PN 结二极管和亚阈值区器件上存在的漏电流功耗;(3) 数字信号上升或下降沿有限时间内的短路电流功耗;(4) 金属-氧化物-半导体(NMOS)形式的逻辑电路中存在的静态偏置功耗.

总功耗  $P_{\text{tot}}$ 包括动态开关功耗 $(P_{\text{sw}})$ 、短路电流功耗 $(P_{\text{sc}})$ 和漏电流功耗 $(P_{\text{L}})$ . 即

$$P_{\text{tot}} = P_{\text{SW}} + P_{\text{SC}} + P_{\text{L}} = P_{\text{t}} (V C_{\text{L}} V_{\text{DD}} f_{\text{clk}}) + I_{\text{SC}} V_{\text{DD}} + I_{\text{L}} V_{\text{DD}}$$

(1)

式(1)中 $:C_L$  是负载电容 $:f_{elk}$ 是时钟频率 $:P_L$  是消耗的功耗的翻转概率:V 是信号的摆幅 $:V_{DD}$ 是电源电压 $:I_L$  是漏电流:V 等于 $:V_{DD}:I_{SC}$  是等效短路电流 $:I_L$  是漏电流 $:I_L$  是源电流

对芯片的测试表明,这3种功耗中起主要作用的是动态开关功耗.基于此,芯片的低功耗设计即在保持电路功能与性能不受影响的条件下,减小芯片的 $P_{\rm t}$ , $C_{\rm L}$ , $V_{\rm DD}$ 和  $f_{\rm els}$ .

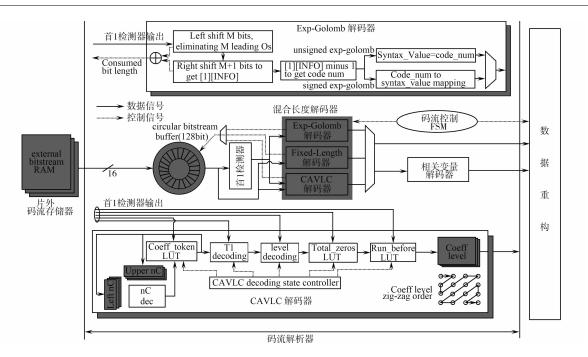

# 2 H. 264 视频解码 IP 核架构

H. 264 视频解码 IP 核主要由码流分析模块和码流重构模块组成,视频解码系统框图如图 1 所示. 其中:码流解析器模块负责处理编码码流中的每个语法元素,并生成相应的参数和控制变量. 根据码流解析器的输出,数据重构模块可以得出残差和预测图像;最后,根据残差和预测图像得到重构的图像.

#### 2.1 码流分析模块设计

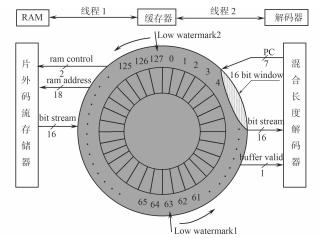

为了降低功率消耗,提出新型的环形码流缓冲结构,可极大减少解码器访问片外存储的次数,从而降低系统功耗.如图 2 所示.缓存器里可保存待处理的 128 bit 码流数据.为了适合混合解码器的不定长

收稿日期: 2010-01-19

通信作者: 凌朝东(1964-),男,副教授,主要从事模拟集成电路的研究. E-mail;edac@hqu. edu. cn.

**基金项目:** 福建省自然科学基金资助项目(T0850005);福建省厦门市科技计划项目(3502**Z**20080010)

图 1 视频解码系统框图

Fig. 1 System architecture of the video decoder

解码,码流缓存器以比特位寻址.环形缓存器有两个线程,用来管理片外码流存储器与环形缓存器 之间、环形缓存器与混合长度解码器之间的通信.

线程1用来控制环形缓存器从片外码流存储器上读取码流数据.在上电复位后,线程1将花4个时钟周期读取64 bit(一半缓存器)的数据到环形缓存器中;然后,一个 buffer\_valid 信号有效,即通知解码器可以从缓存器读取数据了.在以后的连续4个时钟周期,环形缓存器剩余的64位将被填充,同时 buffer\_valid 信号一直保持有效.

用 2 个 Low-Water 标志来防止输入码流的上溢和下溢.它们两个一直指向一个固定的物理地址:0 和 63.当 PC 值超过 Low-Water 标志,即PC 小于 0 或者大于 64 时,线程 1 将被唤醒,用 4

图 2 码流缓存器

Fig. 2 Bitstream buffer

个时钟周期从码流存储器中读取 64 bit 的数据到环形缓存器中;然后,线程 1 进入休眠状态.

线程 2 控制环形缓存器与混合长度解码器之间通信,操作就像一个滑动窗口. 当 buffer\_valid 有效时,在当前窗口里面的 16 bit 码流数据被读取到混合长度解码器中进行处理,之前被解码的码流数量通过 PC 值输出,指示下一个新的窗口的位置. 两个相互独立的线程使码流缓存器的写入与读取也是相互独立的. 从外面表现出来的状态就像一个无限大的缓存器,为解码器提供连续不断的码流.

#### 2.2 基于统计的首"1"检测器设计

在混合长度解码器中,Exp-Golomb 解码器的解码首先要识别 Exp-Golomb 编码的每个码字中第 1个出现"1"位置. 传统的解析器通常不考虑功率消耗问题. 例如,把 16 bit 数据分成 4 个部分(每个向量 4 bit),每个向量都要检测输入的 4 bit 数据中是否有"1";然后,检测的结果决定哪个向量进入下一步测试. 尽管这种设计工作的很好,但是它不是一个节省功耗的设计,因为它对每个 16 bit 都同样对待.

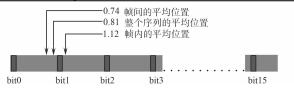

在此,提出一个低功耗首"1"(第 1 次出现"1")检测器,它利用了码字统计分布规律.通过模拟的输入码流,可以得到首"1"出现在不同位置的统计分布情况,如表 1 所示.表 1 中: $\varphi_{tot}$ , $\varphi_{t}$ , $\varphi_{e}$ 分别为整个输入码流,帧内编码帧和帧间编码帧的分布率.根据表 1 原理,码流中第 1 个"1"的位置大致如图 3 所示.

整个视频流、帧内、帧间第 1 个"1"的位置分别是 0.81, 1.12, 0.74, 这比参考文献[5]中的平均数 8.5 小很多.需要说明的是, 位置是整数, 数字只是个平均数.

表 1 首"1"位置统计分布情况

| 位置 | $arphi_{ m tot}$ / $^0\!\!/_0$ | $arphi_{ m i}$ / $rac{9}{6}$ | $arphi_{ m e}$ / $rac{9}{10}$ | 位置 | $arphi_{ m tot}$ / $^0\!\!/_0$ | $arphi_{ m i}/\%$ | $arphi_{ m e}$ / $^{0}\!\!/_{0}$ | 位置 | $arphi_{ m tot}/\sqrt[9]{_0}$ | $arphi_{ m i}$ / $^0\!\!/_{ m 0}$ | $arphi_{ m e}$ / $rac{\%}{0}$ |

|----|--------------------------------|-------------------------------|--------------------------------|----|--------------------------------|-------------------|----------------------------------|----|-------------------------------|-----------------------------------|--------------------------------|

| 0  | 55.36                          | 51.37                         | 56.61                          | 5  | 0.88                           | 1.60              | 0.65                             | 10 | Nearly0                       | Nearly0                           | Nearly0                        |

| 1  | 24.15                          | 24.36                         | 24.08                          | 6  | 0.41                           | 0.91              | 0.25                             | 11 | Nearly0                       | Nearly0                           | Nearly0                        |

| 2  | 11.16                          | 10.70                         | 11.31                          | 7  | 0.16                           | 0.40              | 0.08                             | 12 | Nearly0                       | Nearly0                           | Nearly0                        |

| 3  | 5.49                           | 6.21                          | 5.26                           | 8  | 0.06                           | 0.24              | 0.01                             | 13 | Nearly0                       | Nearly0                           | Nearly0                        |

| 4  | 2.17                           | 3.69                          | 1.72                           | 9  | 0.04                           | 0.15              | Nearly0                          | 14 | Nearly0                       | Nearly0                           | Nearly0                        |

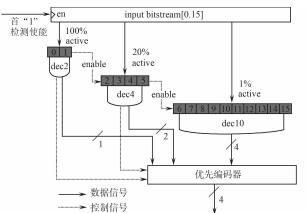

从以上分析,可知第 1 个"1"最有可能出现在位置 2. 开始时,两位占 80%的可能性,前 6 位占了 99%的可能性. 因此,设计中提出一种基于优先级的非均匀分割的首"1"检测方法,输入的 16 位分为 3 个不均匀的子检测器,而每个子检测器可以选择性地启用和关闭,如图 4 所示.

在设计中,从码流缓存器中输入的码流由一

图 3 平均第 1 个"1"的位置 Fig. 3 First '1' of the average position

个使能信号控制. 如果目前的码字需要第 1 个"1"检测,整个 16 位都使能并传送给首"1"检测器;否则,

检测器将关闭,以减少不必要的开关动作,达到节省功耗的目的.整个检测器分为3部分,每个部分随着优先级的不同处理输入码流的不同部分,dec2拥有最高的优先级,处理第0与第1两位输入,并一直检测第首"1"及其相应的可能位置.如果首"1"是发现在 dec2,这个位置信息就被传送到最后的优先级编码器,得出第1个"1"的位置.

为了节省功耗,优先级比较低的 dec4 和 dec10 被关闭. dec2 只有 20%的可能没有检测到首"1"而将 dec4 启用; dec2 和 dec4 只有 1%的可能性没有检测到首"1"而启用 dec10. 采用基于优先级的非均匀分割技术,可达到节省功耗的目的.

图 4 首"1"检测器结构图

Fig. 4 First '1' detector chart

## 3 系统 FPGA 验证

用低功耗技术设计的 H. 264 Baseline 解码 IP 核的 FPGA 验证平台,采用 Stratix EP1S80 DSP+DE2 组成.FPGA 验证占用的逻辑资源,如表 2 所示. 视频解码模块在 Stratix EP1S80 DSP 板上运行, DE2 板作为控制板,负责从 SD 卡读取 H. 264 视频文件送到 Stratix EP1S80 DSP 板进行解码,生成YUV 格式视频;然后,经过 YUV2RGB 转换成 RGB 格式视频在 LCD 上显示.

表 2 FPGA 验证占用逻辑资源情况

Tab. 2 Logic resources on the FPGA verification

| Туре                     | STRATIX EP1S80B956C6 | CYCLONE [ EP2C356F672C6 |  |  |  |

|--------------------------|----------------------|-------------------------|--|--|--|

| Total logicelements      | 39664/79040          | 7692/33212              |  |  |  |

| Total pins               | 39/692               | 56/475                  |  |  |  |

| Total memory bits        | 21248/7427520        | 119296/483840           |  |  |  |

| DSP block 9-bit elements | 8/176                | 8/176                   |  |  |  |

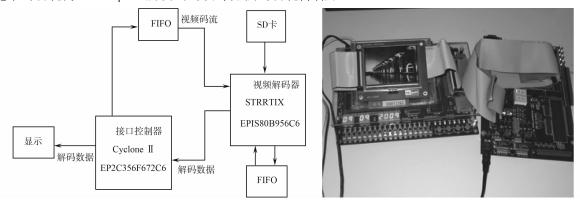

图 5 为验证平台的系统框图,图 6 是低功耗 H. 264 Baseline 解码 IP 核的 FPGA 验证平台. 实验结果表明,在 14 MHz 系统工作频率的情况下,H. 264/AVC BaselineQCIF 解码速度达到 30 帧  $\cdot$  s<sup>-1</sup>,可满足实时解码需求. 由 Power Compiler 软件进行功耗分析,该 IP 核实时解码功耗为 918  $\mu$ W,参考文

[6]中的功耗为  $1644 \mu W$ ,所提出的设计方法的功耗降低了 44%.

图 5 FPGA 验证系统框图

Fig. 5  $\,$  Block diagram of FPGA verification system

图 6 系统 FPGA 验证平台 Fig. 6 FPGA verification platform

### 4 结束语

在深入研究 H. 264 视频编码标准的基础上,采用 Verilog-HDL 语言设计了一款适用于移动终端设备的低功耗 H. 264 baseline 解码 IP 核. 软件仿真和 FPGA 验证结果表明,该 IP 核功耗为 918  $\mu$ W,降低了 44%,可达到实时解码需求,在手机或 MP4 等移动终端有广泛应用前景.

#### 参考文献:

- [1] LIU T M, LEE C Y. Memory-hierarchy-based power reduction for H. 264/AVC video decoder [C] // IEEE International Symposium on VLSI Design, Automation and Test, 2006:1-4.

- [2] 吴继华,王诚.设计与验证 Verilog HDL[M]. 北京:人民邮电出版社,2006.

- [3] 凌朝东,刘蓉,林旭.用 CPLD 实现的 FIR 滤波器[J]. 华侨大学学报:自然科学版,2001,22(1):76-79.

- [4] 毕厚杰. 新一代视频压缩编码标准: H. 264/AVC [M]. 北京:人民邮电出版社,2005.

- [5] LIN Ting-an, LIU Tsu-ming, LEE Chen-yi. A low-power H. 264/AVC decoder [C] // IEEE International Symposium on VLSI Design, Automation and Test, 2005; 283-286.

- [6] CHEANG H C, LIN C C, GUO J I. A novel low-cost high-performance VLSI architecture for MPEG-4 AVC/H. 264 CAVLC decoding [C] // IEEE International Symposium on Circuits and Systems. Kobe: [s. n. ], 2005;6110-6113.

### Design of Low-Power H. 264 Baseline Decoder IP Core

ZHU Kun-wang<sup>1,2</sup>, FU Wen-yan<sup>1,2</sup>, LING Chao-dong<sup>1,2</sup>

College of Information Science and Engineering, Huaqiao University, Quanzhou 362021, China;

Key Laboratory of ANSIC and System, Xiamen 361008, China)

**Abstract:** Using the structure with circular bitstream buffer and the first '1' detection method and priority non-uniform segmentation to design a low-power H. 264 baseline video decoder IP core, and software simulation and field programmable gate array (FPGA) verification is investigated. The results show that the IP core's power consumption is 918  $\mu$ W, decreased 44%. H. 264/AVC baseline QCIF decoding speed meet the needs of real-time decoding of 30 • s<sup>-1</sup>.

Keywords: H. 264 decoder; IP core; low-power; field programmable gate array

(责任编辑: 陈志贤 英文审校: 吴逢铁)