# 双测频链有效减少±1误差在测频中的影响\*

## 戴在平 潘敦

(华侨大学电子工程系,泉州 362011)

摘要 介绍利用单片机的计算和控制能力,采用两个测频计数链,以消除一般测频产生的士1 误差的实现方法.

关键词 测频计数链, ±1 误差, 主闸门控制 分类号 TM 930.9

现代测量技术对信号的精确性和稳定性测量提出了更高的要求.在一般频率测量中,普遍存在着由于被测频率与量化基准频率的相位不同步而产生的 $\pm 1$  测量误差<sup>①</sup>.即使是价格昂贵、电路复杂的专用测频计,通常也存在着测频计数的 $\pm 1$  误差.一般改善 $\pm 1$  误差的代价就是采取舍去有效位来消除 $\pm 1$  误差<sup>②</sup>,但若能使量化基准频率始终自动与被测频同步变化,则 $\pm 1$  的误差就不复存在.为此,提出一种以单片机为主控,并经数据处理而计算得到高精度的频率值的方法.该测量电路是由可编程定时/计数器 8253 和 D 触发器,以及通用门电路组成的具有反馈控制的两个测频计数链.其被测频率计数链是与被测  $f_x$  同步,而基准频率计数链与单片机的主频相关同步,从而使得两个测频链不产生 $\pm 1$  误差.同时,还可利用单片机的数据处理能力来降低测量误差、进行自动测试和显示测量结果.

## 1 测频的工作原理

通常数字式测频和测周期,实质就是对频率与时间进行量化,把被测频率  $f_x$  与基准频率  $f_0$  之比取整,即为量化数字  $N=(f_x/f_0)\pm 1^{(1)}$ . 其中 $\pm 1$  的误差即是  $f_x$  与  $f_0$  或  $T_x$  与  $T_0$  相位上不同步的情况。由于  $f_x$  或  $T_x$  是变化的,所以,测量精度会受到影响。如果采用单片机控制双计数链相关测频,就能使主闸门控制时间与  $f_x$  同步,而基准频率又与单片机主频是相关同步的。当单片机发出主控时间闸门信号,与  $f_x$  经 D 触发器进行同步产生主闸门控制信号,并开启被测频计数链和基频测频计数链,使两条计数链同时计数。 待至一定的定时时间,单片机主控时间闸门信号关闭,则该信号与  $f_x$  同步后,产生主闸门控制信号同时关闭两条计数链,此时被测频计数链的定时时间  $(T=N_0/f_0)$  是相同的。因此有  $T=N_2/f_x=N_0/f_0$ ,即  $f_x=f_0N_2/N_0$ ,其中  $N_2$  为被测频计数链的计数值, $N_0$  为基频测频计数链的计数值;若  $f_0$  是基频频率,则  $f_x$  就是被测频率.

由于主闸门控制与  $f_x$  是同步的,且开门时间与被测信号的周期是整数倍的关系,所以,被

<sup>\*</sup> 本文 1996-11-26 收到; 国务院侨办重点科研基金资助项目

测频计数值是不会产生 $\pm 1$  误差的. 而主闸门控制时间虽可能与 $f_0$  出现偏差,但只要  $N_0\gg 1$ ,则因  $N_0$  所产生的 $\pm 1$  误差与  $f_x$  成反比,比起与  $f_x$  成正比的  $N_2$ ,其对测量精度的影响更小.

## 2 测频系统的硬件组成

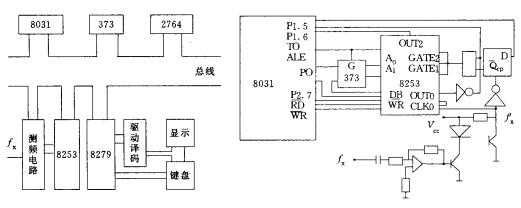

整个测频系统的硬件原理框图如图 1 所示. 系统由三个部分组成:(1) 以 8031,74 LS 373 和 2764 EPROM 组成的 MCS-51 最小系统,承担着主控命令、状态检测和数据处理任务;(2)以8279为主的链盘/显示部分,承担着人机对话和显示测量结果的工作;(3)以8253定时/计数器为中心的测频电路则组成两条测频计数链<sup>(3)</sup>. 本文仅对被测频率范围在 0~2 MHz 的信号进行讨论.

由 8253 组成的两条测频计数链对  $f_x$  测量的实现 · 如图 2 所示 · 本系统的主频时钟为 6 MHz,那么 8031 的 ALE 引脚就可产生 1 MHz 作为基准频率  $f_0$  8253 芯片包括 3 个 16 位计数器,分别有独立的门控(GATE)、输入(CLK)和输出(OUT)端口 · 将计数器 0 与计数器 1 串接成被测频计数链,以检测  $f_x$ ,而将计数器 2 与 8031 中的计数器 0 串接成基频测频计数链,以检测基频  $f_0$ ,从而组成本系统测频的双计数链 ·

图1 硬件原理框图

图2 测频计数链硬件接线

8253 具有 6 种工作方式,现将计数器 0,2 编程设定为工作方式 2. 在此工作方式下,计数器装入计数初值 N,且门控为高电平(门控开启状态),此时开始工作.即当 CLK 端下降沿到来时,计数器作减 1 操作;当计数器回零,则 OUT 端输出一负脉冲,其脉宽为 1 个 CLK 周期,同时计数器恢复初值,以便下一轮的计数工作.再将 8253 的计数器 1 设置成工作方式 0,OUT 端输出低电率,在门控允许的情况下,赋初值后计数器便开始工作.若 CLK 端出现下降沿,到计数器自动减 1,而 OUT 端保持输出低电平;当计数回零,则 OUT 端变为高电平输出,并保持到重置初值或重写工作方式 0 控制字.

实现  $f_x$  的测量,只需确定  $f_0=1$  MHz,在主控时间闸门信号的一定范围内从两条测频计数链上读取  $N_1$  和  $N_2$ ,通过计算  $f_x=f_0$   $N_2/N_0$  可得到  $f_x$  的测量结果 . 如图 2 所示,系统工作过程是单片机的 P1.5 发出主控时间闸门信号(低电平有效)接 D 触发器的 D 端,当  $f_x$  经滤波放大整形后得到同频率的  $f_x$ ,取反后接 D 触发器的 CP 端 . 所以,当  $f_x$  出现下降沿时,D 触发的 CP 端为上升沿,此时 D 触发器开启其  $\overline{Q}$  端输出高电平 . 这时,由于 8253 的计数器不可能减 1 回零,所以,OUT1 必定为低电平,取反后为高电平 . 两者相与后主闸门控制信号,它与

$f_{x}$  是同步动作的,并使  $f_{x}$  被测频计数链与  $f_{0}$  基频测频计数链同时工作  $\cdot$   $f_{0}$  和  $f_{x}$  使 8253 的 计数器 2 和计数器 0 减回零,也使单片机的 CT0 和 8253 的计数器 1 分别得到一个负脉冲,从而进行计数工作  $\cdot$  由于 4 个计数器都是 16 位计数器,所以,两条计数链均可实现 32 位计数,从而保证有十进制数的十位有效位  $\cdot$  当 8031 的 P 1  $\cdot$  5 端发出主控时间闸门信号时间到  $\cdot$  P1  $\cdot$  5 端发出主控时间闸门信号时间到  $\cdot$  P1  $\cdot$  5 二 1),不能马上关闭 8253 的 3 个计数器  $\cdot$  必须待  $f_{x}$  下降沿到来,使 D 触发器 CP 端得到上升沿  $\overline{Q}=0$ ,才能与  $f_{x}$  同步地关闭 GATE0~GATE2,从而使 8253 与单片机组成的双测频计数链停止计数  $\cdot$

由于  $f_0=1$  MHz 且  $N_{0\text{max}}=2^{32}$ ,所以,总可选取时间 T,使得  $f_0$  的基频测频计数链不溢出。在 T 时间内,被测频计数链有两种情况:(1)  $N_2$  在一般计数值域内,只要取得两计数链的  $N_0$ , $N_2$  即可计算  $f_{\text{x}}$ ;(2)  $N_2$  计数链产生溢出,则它在溢出的  $\tau$  时刻,8253 的计数器 1 因工作在中断方式.此时,OUT1 由低变高,取反后即由高度低,使得 GATE0~GATE2 由高变低而关闭了两条计数链.因此, $N_0$  的数据不再变化,即使延长 T- $\tau$  时间,双计数链的取值也是  $\tau$  时刻值,此时  $f_{\text{x}}=\frac{2^{32}}{N_0}f_0$ ;而如果  $f_{\text{x}}$  是处于超低频频率段,则因双计数链的关闭是与  $f_{\text{x}}$  同步,可能导致  $f_0$  基频测频链计数值  $N_0$  的溢出.即使如此,也无妨,因为,单片机 CT0 溢出中断时,就有  $f_{\text{x}}=\frac{N_2}{2^{32}}f_0$ .当  $N_2$ >1 时,可适当减少 T 值,以求得精度较高的  $f_{\text{x}}$ ;当  $N_2$ =1 时,则可视为测频下溢  $f_{\text{x}}<\frac{1}{2^{32}}\times 1$  MHz $\approx 2$ .  $3\times 10^{-4}$  Hz,此时被测信号是直流信号.

## 3 系统软件设计

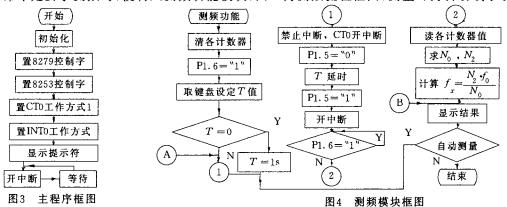

测频系统一般仅作为子系统,所以在此仅简介相关的程序框图,图 3 为主程序模块. 初始 化包括堆栈设置、相关自检和  $f_0$  自检 .8279 (口地址  $0BFF0_H \sim 0BFF1_H$ )设置为 16 位 LED 显示和编码双键互锁键盘工作方式,以提供高精度的显示条件,8253 (口地址  $7BFF0_H \sim 7BFF3_H$ )设置各计数器的工作方式;CT0 设置为 16 位计数器工作方式,允许中断,以组成双测频计数链. 当 CT0 溢出中断时, $f_x$  就处于超低频范围,置 INT0 为允许中断,下降沿触发工作方式,以等待键盘或串行口接收命令.

当命令是要求测频时,便转人测频功能模块,图 4 为测频流程框图,测量可为自动或手动

测量.自动测量仅在另一个命令到达时才停止测量;而手动测量则在每一次测量完成并数据

显示后,便跳转到中断等待状态.

测频功能模块包括发送主控时间闸门信号、获取计数链值、计算被测频率  $f_x$  和显示测量结果等部分。由于 8253 的计数器是减法计数器,所以,计数器读数必须求补后才是  $N_2$ ;而单片机内部的 CT0 则是加法计数器,所以,基频测频计数链值是高 16 位直读,低 16 位求补然后组合成  $N_0$ ; $f_0$  是常数可预先定义。为了保证有效位,可以用 5 字节浮点数(单字节阶码、4 字节尾数)运算求得  $f_x$ ,最后再经数制转换而得 BCD 码,并显示该结果。另外,当  $f_x$  在超低频范围时,便可能出现 CT0 溢出中断。若此时  $N_2$ =1,则测量结果清零,并中断返回 B 点;若  $N_2$ >1,则可计算  $T \leq T_0 - T_0/2$ ,其中  $T_0$  为上次定时时间(简单算法可将  $N_2$  与  $T_0$  同时左移至  $N_2$  =0 且使  $T_0$  变为  $T_1$  值,取  $T = T_0 = T_1$  即可满足上面不等式),此后便可中断返回到 A 点以进行更精确的测频。

#### 4 结束语

使用本系统与 8 位数字频率计 GFC-8131 进行比较,在测量范围较大的情况下,显然具有在高频率范围内相对稳定,有效位为 10 位;在中、低频率范围内,有效位明显多于 GFC-8131 等优点.另外,用数字式激励源两者的反应基本一致,而对于模拟激励源,本系统的稳定性优于 GFC-8131.

为了进一步扩大测频范围,可以用 8254-2 替代 8253,其最高输入频率由 2 MHz 提高到 10 MHz. 若欲对超低频段进行测量精度扩展,则可选用多  $f_0$  方式或加长基频测频计数链,从而使  $N_0$  的有效位增加至 5 或 6 个字节. 从硬件的增加或软件的复杂程度上看,这种扩展都不会有太大的难度.

#### 参 考 文 献

- 1 杨大伟.对计数器士1的认识.电子测量技术,1990,(1):46~47

- 2 李成贻.再探数字频率计士1个字误差.电子测量技术,1990,(2):30~32

- 3 薛均义,张彦斌. MCS-51,96 系列单片数型计算机及其应用. 西安:西安交通大学出版社,1990.140~149

## Eliminating the Effect of Error $\pm 1$ on Frequency Measurement by Use Double Frequency Measuring Chain and Its Implementation

Dai Zaiping Pan Dun

(Dept. of Electron. Eng., Huagiao Univ., 362011, Quanzhou)

Abstract The effect of error  $\pm 1$  on frequency measurement can be eliminated by use double frequency measuring chain. This is a method based on computing ability and controlling ability of single chip microcomputer. Its implementation is described in detail.

**Keywords** frequency measurement, error  $\pm 1$ , single chip microcomputer